We have learned the structure of shared memory. Now, let's see the synchronization methods using the shared memory.

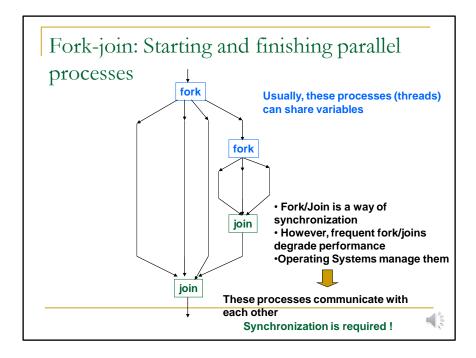

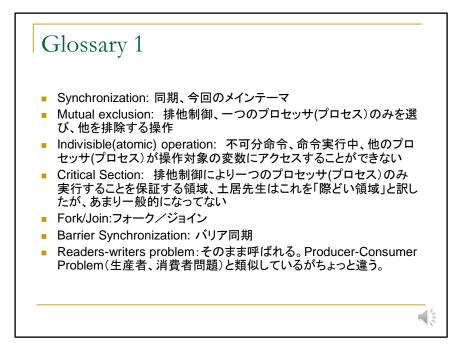

First of all, let's check how we start the parallel processing with the shared memory. Usually, a single process starts, and when it executes fork operation to generate multiple processes. Some child-process can execute fork again. After executing in parallel, all processes execute join operation. At that time, processes except for only a process which executes the fork operation are terminated. When all processes are terminated with the join operation, the total program is finished. This join operation is a kind of synchronization. For example, OpenMP which I will explain in the later class uses this method. That is, parallel programming can be done only with fork-join mechanism. But, since they need heavy overhead, we need other method for synchronization.

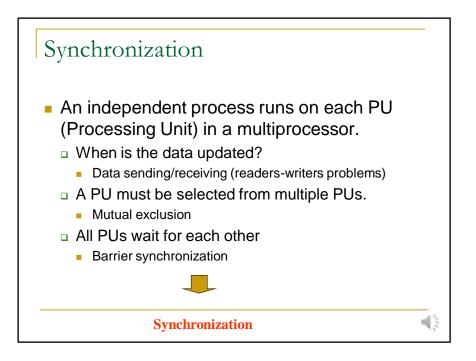

In MIMD processors, an independent process runs on each processing unit. In this case, a processing unit cannot recognize when the data are written into the shared memory from other processing units. Without the synchronization method, data sending/receiving cannot be done. This is called the readers-writers problem. In some cases, a processing unit must be selected from multiple Processing Units. This is called the mutual exclusion. In other cases, all PUs must wait for others. This type of synchronization is called a barrier synchronization.

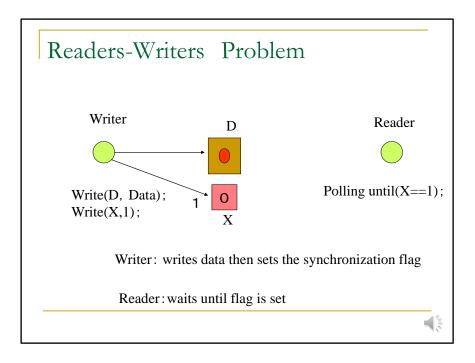

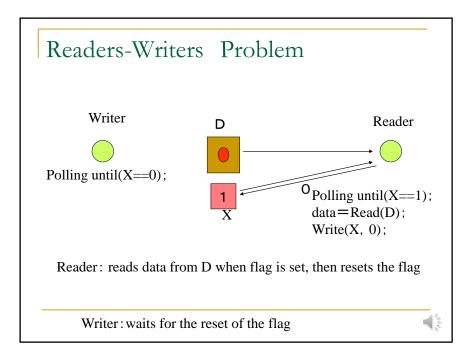

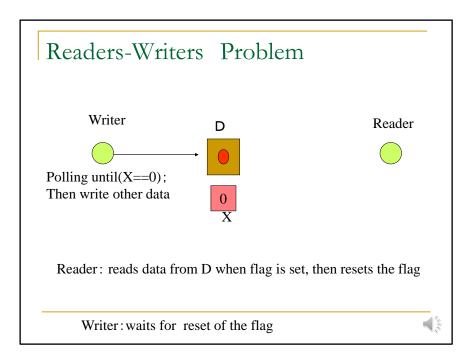

Let me explain the readers-writers problem, first. Assume that a writer wants to send a data block to a reader. In such a case, a writer writes a data into a region in the shared memory. After that it changes the synchronization variable or synchronization flag X into 1. Note that this variable must be initialized to 0.

The reader reads X and if it is 0, it must check again. This operation is called poling or busy waiting. When the reader gets 1, it recognizes the sender has written the data. It reads the data block, then it resets the X into 0.

The writer checks X and if X is 0, it can write the next data if needed.

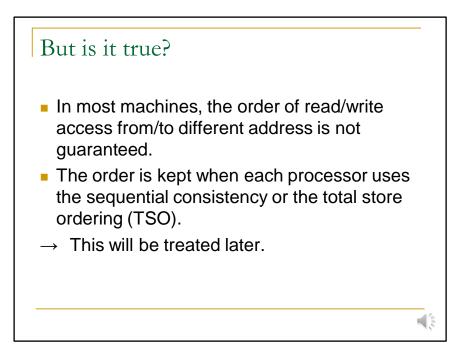

This scenario is true if the order of read/write access from/to different address is guaranteed. Unfortunately, it is not guaranteed in some machines. I will introduce this subject in the next class, but when a processor uses the sequential consistency or the total store ordering (TSO), the scenario is established.

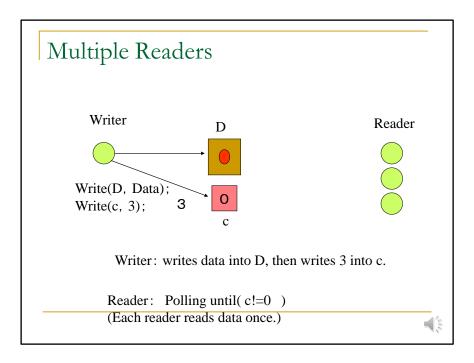

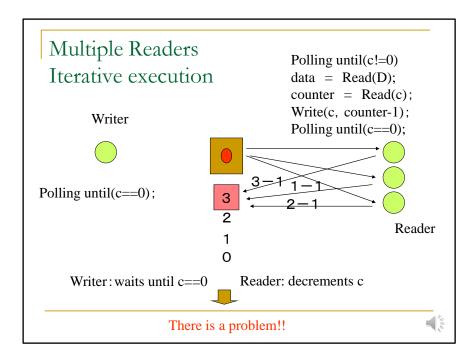

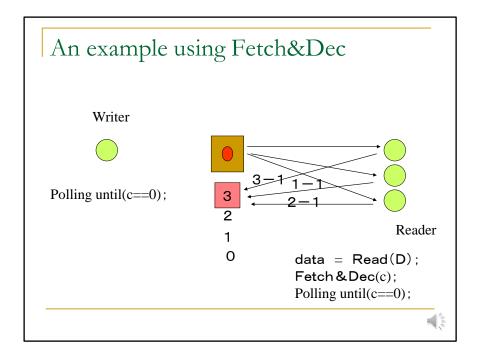

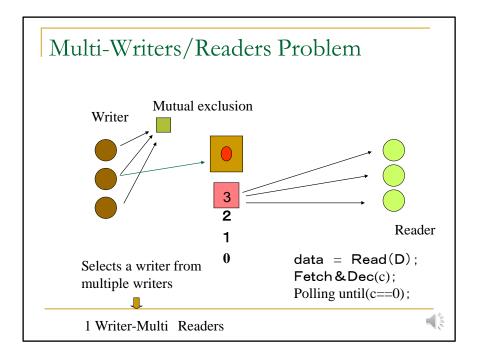

Then, what happens when multiple readers want to receive the data. The simple idea is replacing the synchronization flag X into a counter. When there are three readers, after the write writes the data, it writes a number of readers, three this case, into the counter c.

The reader can recognize that the written data are available. So, after reading the data, it decrements the counter. When all readers finish to read, the counter becomes zero. The writer waits for the counter being zero, and then it writes the next data if needed. This operation seems to work well. But, there is a problem, since it introduces the mutual exclusion problem.

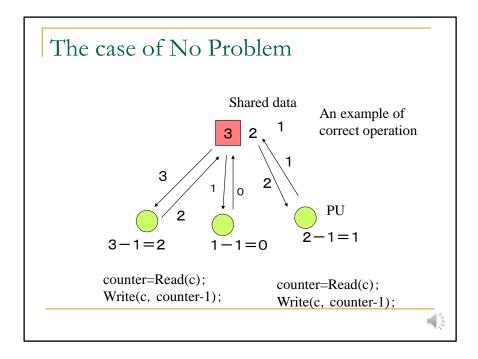

This slide shows the case without any problem. If the Processing Unit accesses the counter in order, it does not cause any problem.

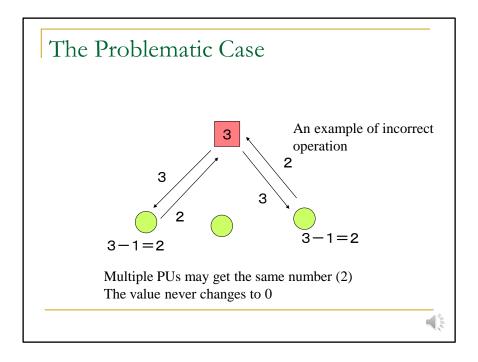

However, what happens when multiple PUs tries to access the counter almost at the same time. When this PU gets three, during it decrements the value, the next PU can read data. It means that two PUs can get the same value 3. In this case, they both write two in the counter, and it never becomes to zero.

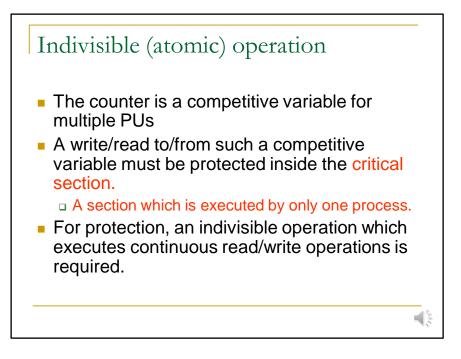

The counter in this example, is called a competitive variable. To such a competitive variable, accesses must be done in the critical section. It means a section which is executed by only a process. This problem can be solved by introducing atomic or indivisible operation.

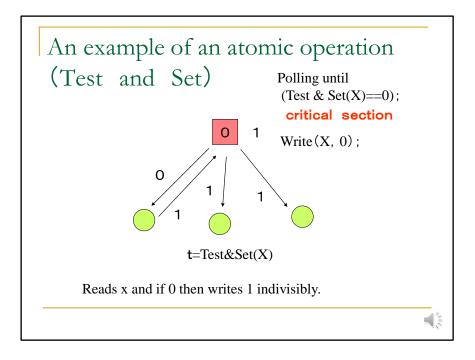

Let me explain the concept of an atomic operation with a simple example Test and Set. This operation reads a variable and writes 1 indivisibly if it is 0. The important point is that reading the data and writing 1 are executed with an action, that is, without interfering by other processors or processes. If multiple processors execute Test and Set to a variable, only one can get 0. It can execute the critical section. After doing it, it must release the critical section by writing 0. Then another processor can get 0 and enter the critical section.

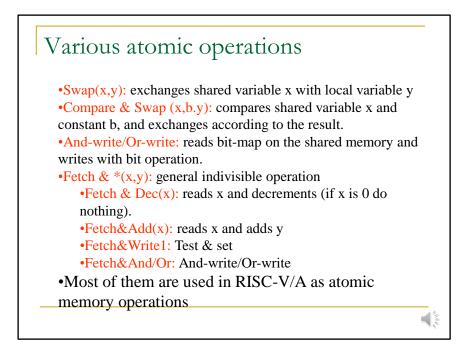

Various atomic operations have been used, and most of them are used in RISC-V as atomic memory operations.

The convenient operation is Fetch&Dec. It reads the data and decrement it indivisibly. The counter can be directly the target of this operation. So, multiple readers problem can be easily solved without using the critical section. The fetch and decrement has two implementations, one is saturated and the other is non-saturated. In the case of saturated, it the reading value is zero, it is not decremented anymore.

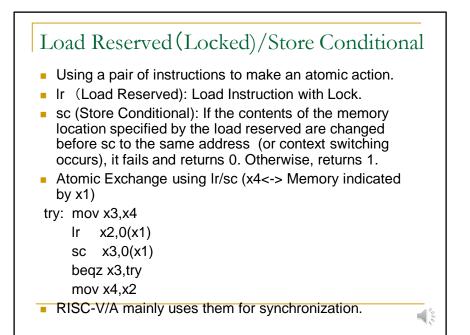

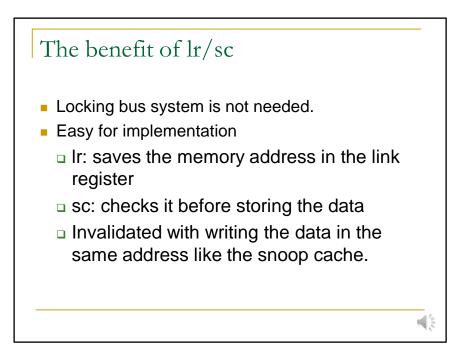

This pair style of synchronization operations load reserved / store conditional has the following benefits.

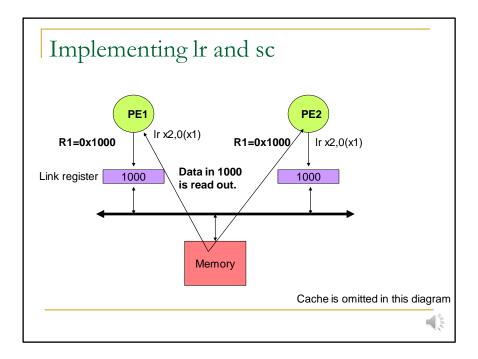

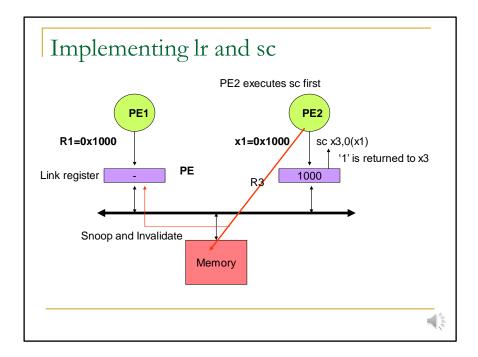

When Ir is executed, the address is set in the link register attached to each processing element.

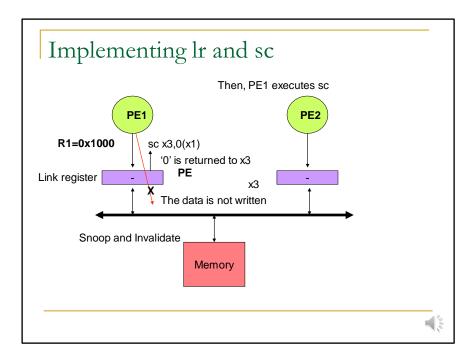

When a PE executes store conditional, the link register is cleared if the address matches. If the link register is alive, it can get 1.

When the other PE executes store conditional operation, it gets 0 since the link register is cleared.

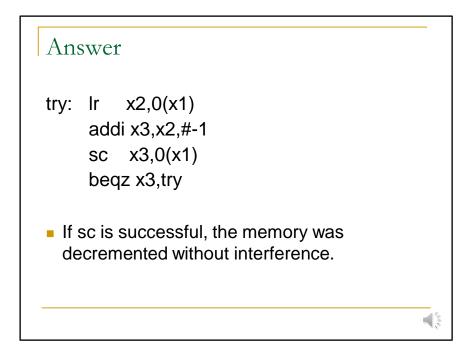

An atomic memory operations can be implanted with a combination of Ir and sc.

This is an answer, if sc is successful, it means that the memory was decremented without interference.

Once the critical section can be used, multi-writers problem can be easily solved. First, a writer is selected with a mutual exclusion operation by using Test and Set for example. Then, the writer executes the single-writer multiple readers problem.

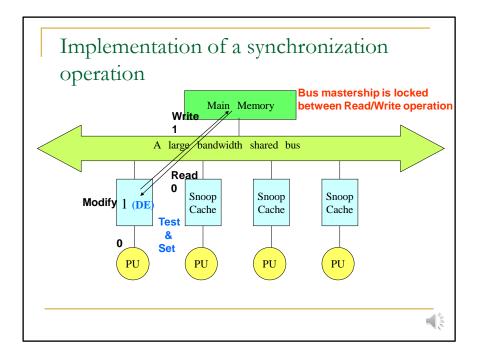

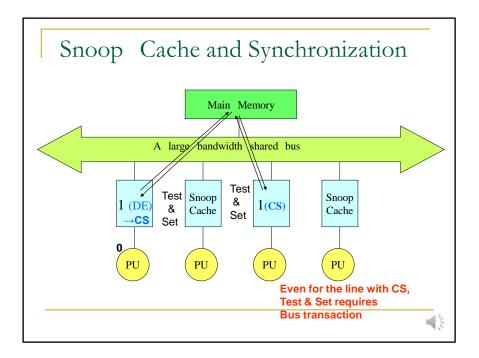

Next, let me explain how the synchronization operations are implemented on the system with private or snoop cache. For example, when Test and Set is implemented on a multi-core system with snoop cache that I explained in the previous class, it will read the main memory and write it locking the bus. Apparently, the value becomes DE since this operation accompanies the write operation.

If multiple PUs try busy waiting, bus will be congested because multiple PUs try to access the bus for the Test & Set operations.

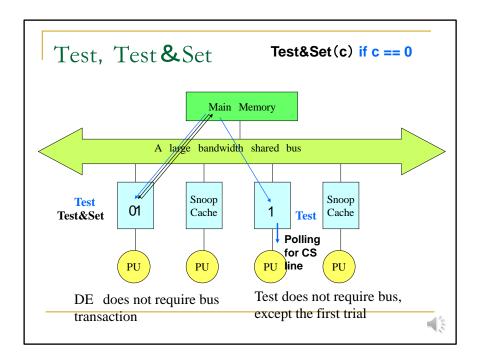

Just by reading the synchronization variable before executing the atomic operation, we can avoid this bus congestion. It is called test test & set. When reading data from the main memory is 1, it is hopeless to try the test and set. In this case, try just reading again.

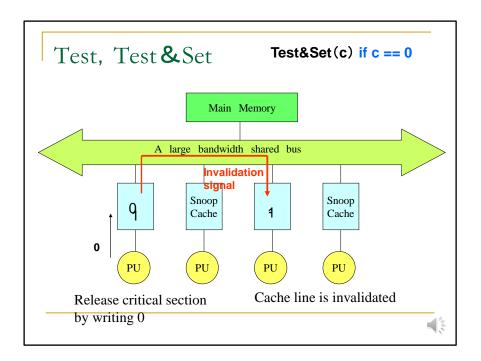

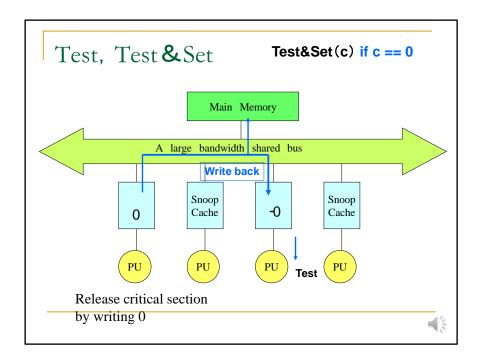

After executing the critical section, a PU writes 0 to release the critical section. At that time, the invalidation signal is transferred on the bus, and other copies are invalidated.

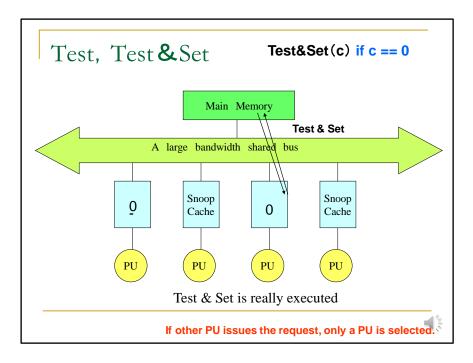

When other PUs reads the synchronization variable. Since it was invalidated, it causes cache-miss, and the value 0 is transferred from the cache which released the critical section. Since the requesting PU gets 0, it executes Test&Set operation. Of course, there may be multiple PUs which get the value 0, but they can be resolved by executing Test&Set.

As a result, only a PU can be selected.

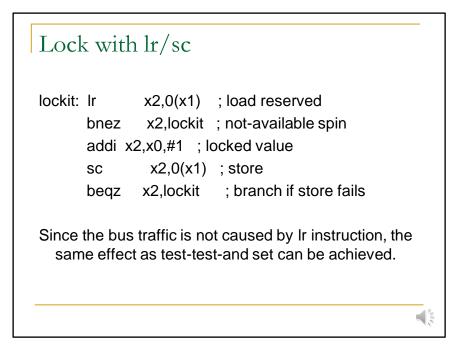

This code is a lock operation by using Ir and sc. Since the bus traffic is not caused by Ir instruction, the same effect as test-test-and-set can be achieved.

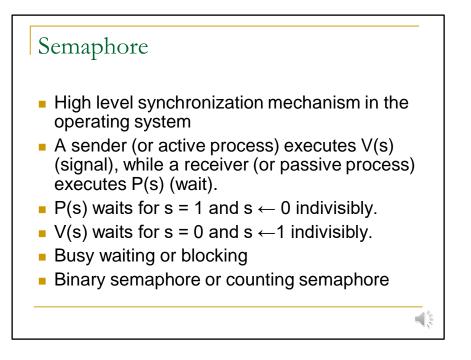

I have introduced basic synchronization mechanisms for multi-cores, but the synchronization operation is needed for operating system which handles concurrent processing of multiple processes. That is, concurrent processes must be treated as the same way of multiprocessors. However, since synchronization operations are implemented mainly with software, sophisticated mechanisms are used. Semaphore is famous synchronization mechanism.

Monitor is also famous example of synchronization. For the safe operation, a set of shared variables and operations to handle them are defined.

Next, let me explain the synchronization memory. Instead of providing atomic operation, the synchronization mechanism can be provided on the memory.

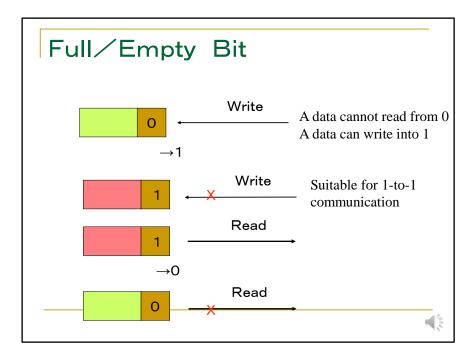

Full/Empty bit is the simplest one. There is a flag for each word of the memory.

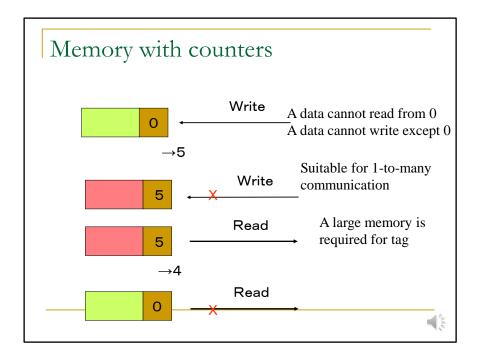

Instead of providing the flag, we can provide the counter.

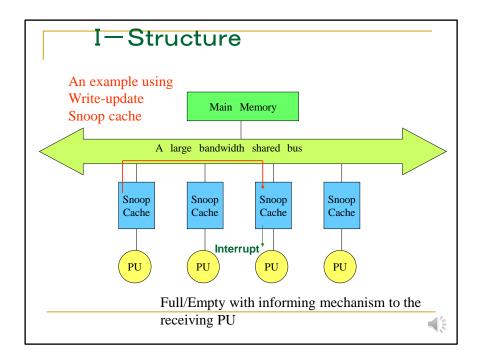

I-structure is a mechanism with informing system with the synchronization memory. This slide shows an example of implementing write-update style snoop cache. This idea was proposed for data flow machines.

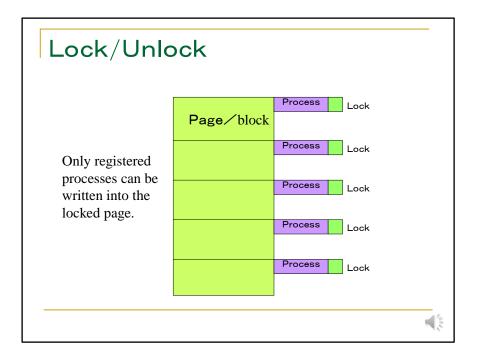

Lock/unlock register can be provided for a certain block of the memory, for example, a page or block of the cache. When a process can write the page when lock bit is not set. At the first write, the lock bit is set and the process number is registered. Only the process whose id matches the register can write the block.

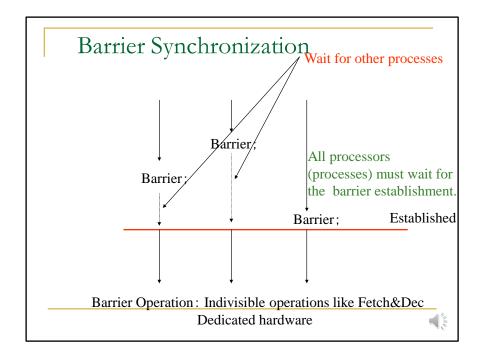

Barrier synchronization is a simple and easy to use. When a processor executes a barrier operation, it must wait other processors execute the barrier operation. When all processors execute the barrier operation, they can go forward. When multiple processors compute different part of a matrix with iteration, after writing results, they execute the barrier operation. When the barrier is established, all results are available, so they can go to the next iteration. Barrier operation can be implemented with atomic instructions, but since it is so popularly used, the special hardware is sometimes provided.

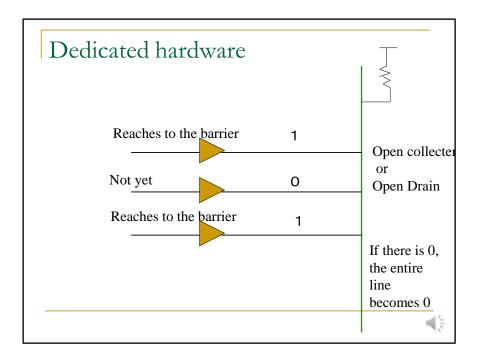

This is an example of the simplest barrier implementation. Only a wire for the open drain output is enough. It is also useful for the debugging.

Extended barrier synchronizations have been proposed.

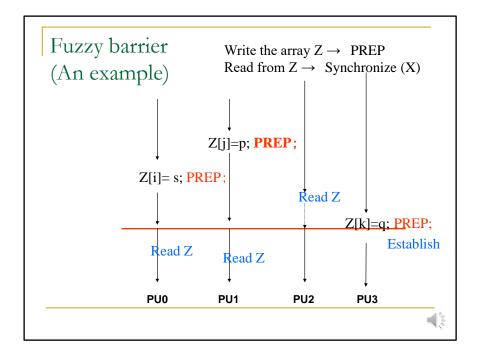

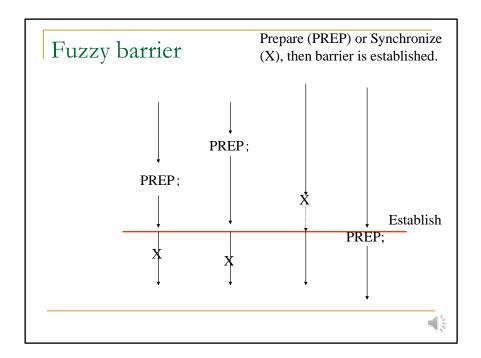

This diagram explains the fuzzy barrier.