Hiroshi Nakahara

Amano Lab , Dept. of Information and Computer Science, Keio University

Email : nakahara_at_am.ics.keio.ac.jp (_at_は@に置き換え)

自己紹介

研究内容

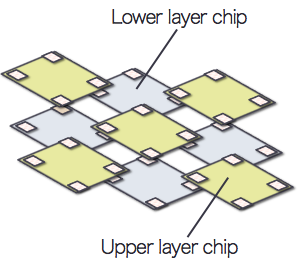

Staggered Stacking (Castle of Chips)

マルチコア・マイクロプロセッサの需要が高まって来たことによって、チップを三次元方向に積層する技術が研究されています。しかし、普通に上方向に積むだけでは物理的な制限のせいで8枚のチップくらいしか積めません。この状況を踏まえて、水平方向にも積層を伸ばすことによってチップの積層枚数を増やすというのがStaggered Stackingという手法です。理論上では、チップを256枚つなげることも可能で、gem5やbooksimというシミュレータで評価を取ったりしています。

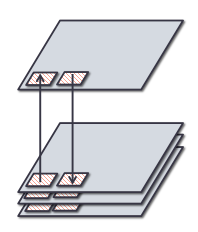

三次元方向のStacking

Staggered Stacking

この研究はまだまだ誰もやっていないので、やれることはたくさんあります。認められるような研究になれるようにもっとがんばります。

経歴

- 2011-03

-

茅ヶ崎北陵高校 卒業

- 2015-03

-

慶應義塾大学 理工学部 情報工学科 卒業

- 現在

-

慶應義塾大学院 理工学研究科 開放環境科学専攻 情報工学専修 在籍

業績

国際会議

- Hiroshi Nakahara, Tomoya Ozaki, Hiroki Matsutani, Michihiro Koibuchi, Hideharu Amano, "Expandable Chip Stacking Method for Many-Core Architectures Consisting of Tiny Chips", Proc. of IEEE 9th International Symposium on Embedded Multicore/Many-core Systems-on-Chip (MCSoC), pp.xxx-xxx, Sep 2015.

- Hiroshi Nakahara, Tomoya Ozaki, Hiroki Matsutani, Michihiro Koibuchi, and Hideharu Amano, "Staggered Stacking : Connecting Many Small Chips Using ThruChip Interface", Proc. of the COOL Chips XVIII (poster), April 2015.

- 中原 浩, 安戸僚汰, 松谷宏紀, 鯉渕道紘, 天野英晴, "三次元積層チップへの高性能既存トポロジレイアウト法", 信学技報, vol. 115, no. 174, CPSY2015-43, pp. 275-280, 2015年8月.

- 中原浩,松谷宏樹,鯉渕道紘,天野英晴,"Castle of Chipsのためのスケーラブルな高性能積層法", 信学技報, vol. 114, no. 330, CPSY2014-79, pp. 39-44, 2014年11月.