MuCCRA group Amano Laboratory, Institute of Science and Technology, Keio University

Greetings! Here is Website of MuCCRA project, AMANO Lab. KEIO University.

About MuCCRA Project

MuCCRA is a researching group about a kind of off-loading processor called “Dynamically Reconfigurable Processor” for media streaming processing.

Specially, our researching aimed to “low-power” for media streaming processing, and DRPs are going to popular in various systems instead of dedicated hardware.

Our group have already developed and evaluated in ASIC of our DRP architectures, and we proposed some features for DRP systems, recently, our interests are Designing architecture of DRPAs, Applying low-power techniques in circuit level, Compiler optimization techniques for DRPAs, Multi-cored DRPA system.

Contents

What is MuCCRA

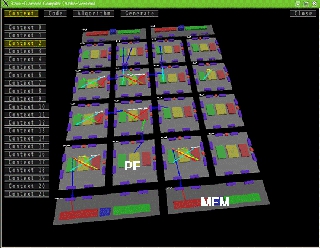

MuCCRA : Multi-core Configurable Re-configurable Architecture is a kind of “Dynamically Reconfigurable Processor”.

- Multi-core : Type of this architecture has many of PE : Processing Elements. Using some of PEs in the same time, processor can processing a great amount of data.

- Configurable : Architecture can changes its achitecture depends on its purposes or application.

- Re-configurable : Change its hardware structure or data-path during execution.

Each PEs are changing its hardware structure every cycle (Called “Context”) to efficient application execution.

Background

Dynamically Reconfigurable Processors be able to achiving low-power and high-performance rather than dedicated hardware such as FPGAs.

Recently, increasing requirements of long battery-life and high performance for embeded applications such as mobile phones, and music player. So, we proposing DRPAs are suitable for those applications.

- DRP is able to cope with various applications with a only one chip.

- Simple hardware can acting comprex hardware with reconfiguration.

- Corse-grained reconfigurable is less overhead than fine-grained reconfiguration such as FPGAs.

Research

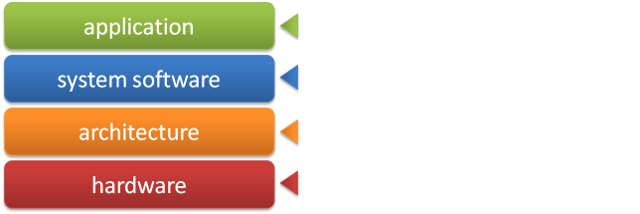

Our group not only researching of architecture level but also circuit level and software level.

- At the circuit level, applying power gating techniques for low power consumption of dynamically reconfigurable processor.

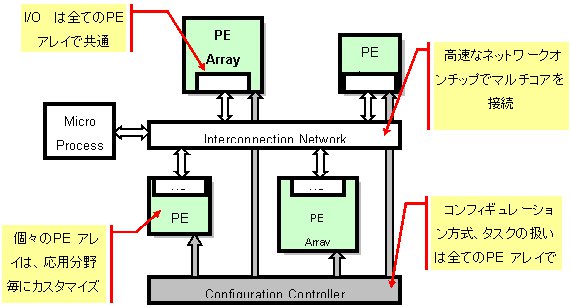

- At the architecture level, researching inter-connection network between PEs, research for multi-core DRP system (Some DRPs are works together).

- At the System software level, we have developed application development environment for MuCCRA-3, researching application mapping algorithm and optimization for perspective of power efficiency.

- At the application software level, we considering what application is suit for this architecture. and improve imprementation of media stream processing.